Intel unveils its long-awaited first 18A chip for data centers

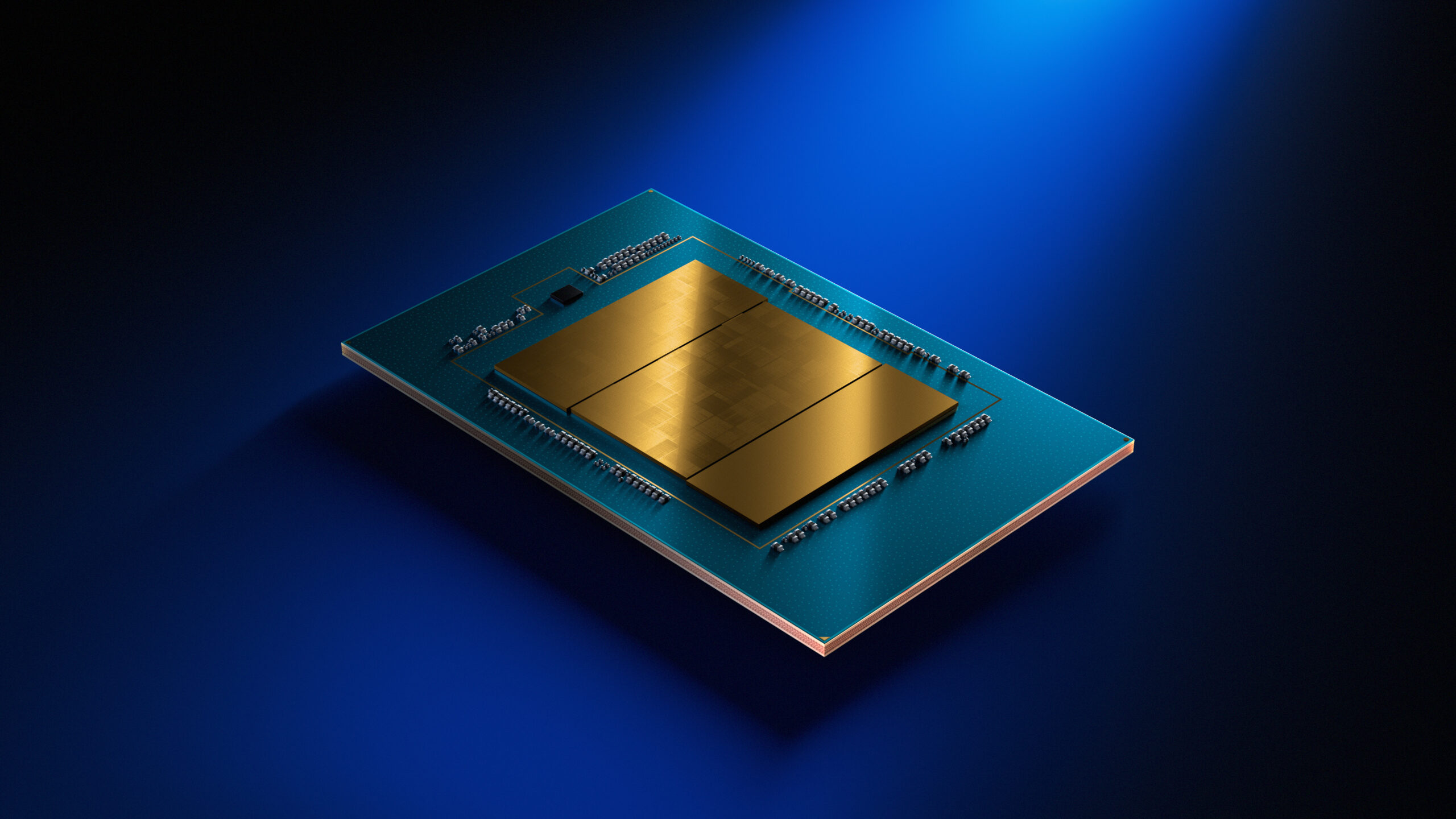

This week, Intel unveiled its Xeon 6+ processors, code-named Clearwater Forest, manufactured on the Intel 18A node, the firm’s most advanced fabrication process and its first design in the 1.8-nanometer class.

The launch highlights a shift in Intel’s strategy for cloud and telecommunications workloads. Instead of prioritizing raw clock speeds, the company is focusing on efficiency, integration, and dense compute capacity.

Clearwater Forest introduces Intel’s new Darkmont efficiency-core microarchitecture. A single processor can contain as many as 288 Darkmont cores, distributed across 12 compute tiles. Each tile houses 24 cores built using the 18A process and connected through Intel’s Foveros Direct 3D stacking technology.

The chip’s design relies heavily on advanced packaging. Communication between the different components is handled by EMIB (Embedded Multi-Die Interconnect Bridge) links, the same interconnect approach Intel uses in its high-end GPU products.

A key objective of the architecture is to minimize latency and power consumption by keeping frequently used data close to the cores. To achieve this, Intel redesigned the cache structure. Groups of four Darkmont cores share a 4 MB L2 cache, while the processor’s last-level cache exceeds 1.1 GB (approximately 1,152 MB), enabling hundreds of cores to access commonly used data without relying heavily on external memory bandwidth.

Despite being built around efficiency cores, the Xeon 6+ platform integrates several accelerators commonly used in modern data-center workloads. These include Intel Advanced Matrix Extensions (AMX) for AI tasks, QuickAssist Technology (QAT) for compression and cryptography, and vRAN Boost, designed for virtualized radio access networks.

These capabilities target telecom and edge deployments supporting 5G Advanced and future 6G infrastructure. By embedding such accelerators directly into the CPU, Intel argues operators can scale AI inference and network processing without adding separate hardware cards.

The platform remains compatible with the existing Xeon socket, simplifying upgrades. It supports 12 channels of DDR5 memory up to 8,000 MT/s and provides 96 PCIe 5.0 lanes, including 64 lanes with CXL 2.0 support. In dual-socket servers, systems can scale up to 576 Darkmont cores.