كيف تمكنت تقنية الشرائح المصغرة (Chiplets) من تحقيق النجاح؟

مقال ضيف بقلم ألكسندر تروشين، مدير تسويق المنتجات في وحدة أعمال الخوادم لشركة AMD في منطقة أوروبا والشرق الأوسط وإفريقيا

ألكسندر تروشين

لعقودٍ طويلة، كان عدد الترانزستورات التي يمكن وضعها على شريحة سيليكون واحدة يخضع لقانون مور، والذي ينص على أنه يمكننا كل عامين تركيب ضعف عدد الترانزستورات على الشريحة، مما يؤدي إلى نمو أسّي في قوة الحوسبة. ومع ذلك، فقد تراجع الاعتماد على قانون مور بشكل ملحوظ في السنوات الأخيرة، مما أجبر قطاع أشباه الموصلات على البحث عن طرق مختلفة لتعزيز أداء وكفاءة وحدات المعالجة المركزية.

شهد العام 2018 أول ظهورٍ لنهج جديد من تصميم الشرائح، والذي حظي بإشادة الخبراء باعتباره طفرة في الصناعة من حيث الأداء وقابلية التوسع؛ حيث طرحت AMD تقنية «chiplet»، أو الشرائح المصغرة الجديدة لأول مرة في معالج خادم EPYC من الجيل الثاني المستند إلى معمارية Zen 2 (المعروفة بالاسم الرمزي Rome)، والذي دخل التاريخ كأول معالجٍ يتميز بنظام وحدة المعالجة المركزية x86 المستند إلى تقنية الشرائح المصغرة فائقة التطور.

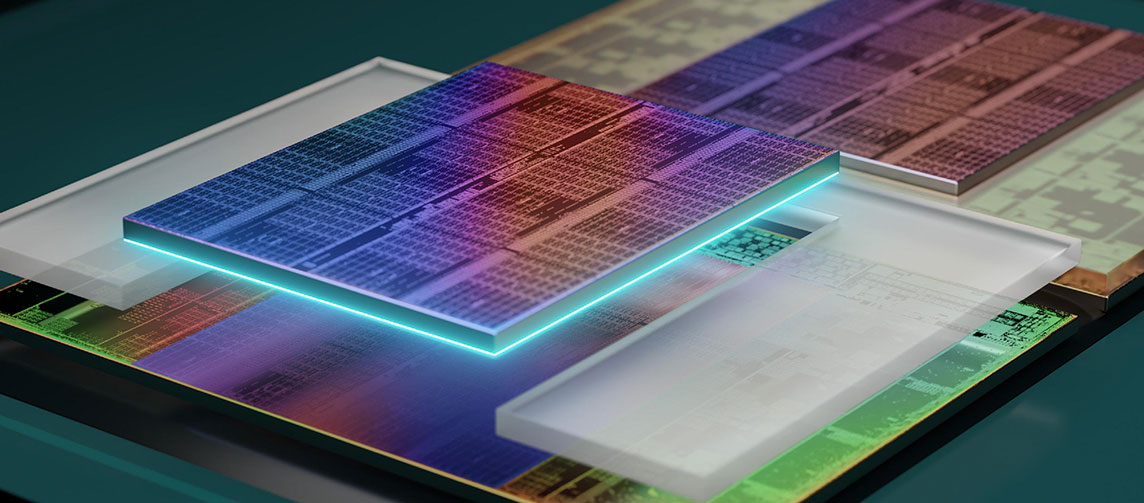

واستناداً إلى مفهوم قديم يرجع إلى عام 1965، فإن نهج الشرائح المصغرة ينص على إمكانية استبدال عملية تصميم شريحة واحدة كاملة، بتصميم مجموعة شرائح من قطع أصغر – أو شرائح مصغرة – يتم بعد ذلك توصيلها معاً لتشكيل شريحة واحدة.

أدّى ابتكار الشرائح المصغرة، التي يشبّهها البعض بقطع الليجو فائقة التطور، إلى حل العديد من المشكلات التي تواجه صناعة أشباه الموصلات؛ حيث يُتيح التحوّل إلى التصميمٍ المُعتمد على تقنية Chiplets خفضَ تكاليف التصنيع، وتمكين مصنّعي الشرائح من ابتكار مجموعات كاملة من منتجات الخوادم دون الحاجة إلى إعادة التصميم ليتناسب مع كل سوق نهائية.

ما هي فوائد تقنية Chiplets؟

تتميز الشرائح المصغرة بكونها شرائح معيارية صغيرة يمكن دمجها لإنشاء حزمة معالج أكبر وأكثر قوة. وبصورة أبسط، يسمح هذا النهج الجديد للشركات باستخدام قالب أصغر بدلاً من قطعة مفردة كبيرة من السيليكون. يُؤدي صغر حجم هذه القوالب إلى تقليل احتمالية حدوث عيوب تصنيعية، ممّا يُتيح استغلال نسبة أكبر من القوالب المنتَجة، وهذا بدوره يؤدي إلى تحسين معدلات الإنتاجية وخفض تكاليف التصنيع، بالإضافة إلى ذلك، تُتيح الشرائح المصغرة للشركات إمكانية تصميم معالجات بقدراتٍ هائلة، فمع إمكانية دمج العديد من الشرائح المصغرة، يمكن تصنيع معالجات بعدد نوىً أكبر، ممّا يُؤدّي إلى تحسين كبير في أداء الحوسبة والذاكرة يفوق بكثير ما يمكن تحقيقه باستخدام شريحة أحادية.

علاوةً على ذلك، تُتيح الـ Chiplets بناء المعالج بطريقة معيارية. على سبيل المثال، في سلسلة معالجات EPYC 7002, 7003، يوجد قالب مركزي للإدخال/للإخراج تحيط به شرائح حوسبة يصل عددها إلى 8، مما يسمح بزيادة عدد نوى وحدة المعالجة المركزية إلى 64 نواة، مع ضمان ملاءمة التكاليف قدر الإمكان بشكل يعزز القيمة للعميل. وفي حال كان عدد النوى لا يتطلب تفعيل الشرائح الثمانية، فسيتم استخدام 2 أو 4 أو 6 شرائح فقط، بحيث لا يدفع العميل تكلفة السيليكون غير المستخدم.

يسمح ذلك أيضاً بتبسيط عمليات التصميم والتصنيع، فمن أجل تصميم مجموعة كاملة من المنتجات يتراوح عدد النوى الخاصة بها من 8 إلى 64، تحتاج AMD إلى إنتاج وحدتين فقط – قالب الإدخال/الإخراج وشريحة الحوسبة، مع إمكانية تركيب عدد مختلف من شرائح الحوسبة حسب الحاجة. وبفضل هذا النهج، تُقلل AMD من تكاليف التصنيع والتصميم بشكل كبير، حيث يتم التركيز على إنتاج عنصرين رئيسيين بدلاً من إنتاج 4 أو 5 عناصر مختلفة لتلبية نفس احتياجات الأداء على الشريحة الأحادية.

لا يوجد أيضاً ما يمنع استخدام الشرائح المصغرة (Chiplets) في حوسبة غير مبنية على نظام x86. فمثلاً، سيكون من الممكن استبدال شريحة نظام x86 بأخرى مصممة خصيصاً كمسرّع للذكاء الاصطناعي، أو وحدة تفريغ الشبكة، أو أي جهاز متخصص آخر. يفتح هذا المجال إمكانات هائلة لمواجهة أعباء العمل الجديدة، دون المساس بمتطلبات الحوسبة الأساسية التي يرغب بها العملاء.

هناك آلية حزم متطورة أُخرى يمكن توظيفها لرفع مستوى الأداء، وهي تكديس القوالب. تتيح هذه الآلية تكديس القوالب عمودياً فوق بعضها البعض، بدلاً من توزيعها على نفس الحزمة مع توصيلات أطول بينها. وهذا يقلل زمن الاستجابة ويحسّن الأداء. ولطالما كانت AMD رائدة في تقنيات تكديس القوالب، حيث قدّمت تقنية 3D V-Cache، والتي تستخدم قالباً مكدساً لمضاعفة مساحة ذاكرة التخزين المؤقت L3 على وحدة المعالجة المركزية.

ما هو مستقبل تقنية Chiplets؟

شهدت صناعة أشباه الموصلات ثورة تقنية هائلة مع إطلاق AMD لجيلها الثاني من معالجات EPYC قبل خمس سنوات. وعلى الرغم من أن هذا النهج كان جريئاً في ذلك الوقت، إلا أنه أثبت أنه خطوة حاسمة في طريق المستقبل. فقد أدركت العديد من الشركات الرائدة في قطاع أشباه الموصلات محدودية التصاميم الأحادية التقليدية، وبدأت في تبني نهج الشرائح المصغرة لمنتجاتهم.

نشهد اليوم دخول نهج الشرائح المصغرة (Chiplets) عالم الحواسيب الفائقة؛ وخير مثالٍ على ذلك حاسوب “فرونتير”، أسرع حاسوب فائق في العالم حالياً، والذي تم تصميمه باستخدام وحدة معالجة مركزية تعتمد على شرائح صغيرة، مما سمح له بأن يكون أول حاسوب فائق يتخطى حاجز إكسافلوب (Exaflop) في الأداء. أمّا بالنسبة لحاسوب “إيل كابيتان” الفائق، فسيستخدم وحدات المعالجة المركزية ووحدات معالجة الرسومات المبنية على تقنية Chiplet، ومن المتوقع أن يتجاوز أداؤه عتبة 2 إكسافلوب. يفتح هذا النهج الجديد في تصميم الشرائح الباب أمام فئة جديدة من الأنظمة التي ستستمر في رفع مستوى الأداء في المجالات المتطورة، ولاستكمال الصورة الواقعية، فإن 4 من أفضل 10 حواسيب فائقة على مستوى العالم تعتمد حالياً على حلول مبنية على شرائح AMD EPYC الصغيرة.

لم يقتصر تأثير ثورة الشرائح المصغرة على الحواسيب الفائقة، بل وصل إلى الأجهزة التي نستخدمها بشكل يومي. فبدأ مصنّعو الشرائح في تبني هذا النهج في تصميم بطاقات الرسومات، مستفيدين من قابليتها للتطوير وسهولة تطبيقها على مختلف القطاعات.

ما الذي يخبئه المستقبل إذن؟ مع انتشار اعتماد نهج Chiplets، برزت الحاجة إلى معيار موحّد يربط هذه الشرائح التي تصنّعها شركات مختلفة. ولهذه الغاية، تم طرح Universal Chiplet Interconnect Express (UCIe)، وهو معيار مفتوح يدعمه العديد من كبار مصنعي الشرائح، بما في ذلك AMD، وله القدرة على إعادة تشكيل تصميمات جديدة لأشباه الموصلات. ويهدف هذا المعيار إلى تمكين صانعي الشرائح من دمج ومطابقة خصائص السيليكون من موردين مختلفين ضمن حزمةٍ واحدة.

وبغض النظر عن الابتكارات التي ستبصر النور قريباً، يبدو جلياً أن طرح تقنية الشرائح المصغرة سيُواصل تحفيز صناعة أشباه الموصلات على الابتكار والإبداع.